Instrukcja obsługi Microchip PIC24F32KA304

Microchip

Niesklasyfikowane

PIC24F32KA304

Przeczytaj poniżej 📖 instrukcję obsługi w języku polskim dla Microchip PIC24F32KA304 (28 stron) w kategorii Niesklasyfikowane. Ta instrukcja była pomocna dla 6 osób i została oceniona przez 2 użytkowników na średnio 4.5 gwiazdek

Strona 1/28

© 2006 Microchip Technology Inc. Advance Information DS39703A-page 2-1

CPU

2

Section 2. CPU

HIGHLIGHTS

This section of the manual contains the following topics:

2.1 Introduction .................................................................................................................... 2-2

2.2 Programmer’s Model...................................................................................................... 2-4

2.3 Software Stack Pointer................................................................................................... 2-7

2.4 CPU Register Descriptions .......................................................................................... 2-10

2.5 Arithmetic Logic Unit (ALU).......................................................................................... 2-13

2.6 Multiplication and Divide Support................................................................................. 2-14

2.7 Compiler Friendly Architecture..................................................................................... 2-17

2.8 Multi-Bit Shift Support .................................................................................................. 2-17

2.9 Instruction Flow Types ................................................................................................. 2-18

2.10 Program Flow Loop Control ......................................................................................... 2-20

2.11 Address Register Dependencies ................................................................................. 2-22

2.12 Register Maps.............................................................................................................. 2-25

2.13 Related Application Notes............................................................................................ 2-26

2.14 Revision History........................................................................................................... 2-27

PIC24F Family Reference Manual

DS39703A-page 2-2 Advance Information © 2006 Microchip Technology Inc.

2.1 INTRODUCTION

The PIC24F CPU module has a 16-bit (data) modified Harvard architecture with an enhanced

instruction set. The CPU has a 24-bit instruction word with a variable length opcode field. The

Program Counter (PC) is 24 bits wide and addresses up to 4M x 24 bits of user program memory

space. A single-cycle instruction prefetch mechanism is used to help maintain throughput and

provides predictable execution. All instructions execute in a single cycle, with the exception of

instructions that change the program flow, the double-word move (MOV.D) instruction and the

table instructions. Overhead-free program loop constructs are supported using the REPEAT

instructions, which are interruptible at any point.

The PIC24F devices have sixteen, 16-bit working registers in the programmer’s model. Each of

the working registers can act as a data, address or address offset register. The 16th working

register (W15) operates as a Software Stack Pointer for interrupts and calls. The 15th working

register (W14) can be used as a Stack Frame Pointer when used with instructions.LNK and UNLK

The upper 32 Kbytes of the data space memory map can optionally be mapped into program

space at any 16K word program boundary defined by the 8-bit Program Space Visibility Page

(PSVPAG) register. The data to program space mapping feature lets any instruction access pro-

gram space as if it were data space. Refer to Section 4.4 “Program Space Visibility from Data

Space” for more information on Program Space Visibility.

The Instruction Set Architecture (ISA) is significantly enhanced beyond that of the PIC18F but

maintains an acceptable level of backward compatibility. All PIC18F instructions and addressing

modes are supported either directly or through simple macros. Many of the ISA enhancements

are driven by compiler efficiency needs.

The core supports Inherent (no operand), Relative, Literal and Memory Direct Addressing

modes, and 3 groups of addressing modes (MODE1, MODE2 and MODE3). All modes support

Register Direct and various Register Indirect Addressing modes. Each group offers up to seven

addressing modes. Instructions are associated with predefined addressing modes depending

upon their functional requirements.

There is also a ‘Register Indirect with Signed 10-Bit Offset’ Addressing mode dedicated to two

special move instructions, LDWLO and STWLO. Refer to Section 32. “Instruction Set” for more

details.

For most instructions, the core is capable of executing a data (or program data) memory read, a

working register (data) read, a data memory write and a program (instruction) memory read per

instruction cycle. As a result, three parameter instructions can be supported, allowing A + B = C

operations to be executed in a single cycle.

A high-speed, 17-bit by 17-bit multiplier is included to significantly enhance the core arithmetic

capability and throughput. The multiplier supports Signed, Unsigned and Mixed mode, 16-bit by

16-bit or 8-bit by 8-bit integer multiplication. All multiply instructions execute in a single cycle.

The 16-bit ALU is enhanced with integer divide assist hardware that supports an iterative

non-restoring divide algorithm. It operates in conjunction with the REPEAT instruction looping

mechanism, and a selection of iterative divide instructions, to support 32-bit (or 16-bit) divided by

16-bit integer signed and unsigned division. All divide operations require 19 cycles to complete,

but are interruptible at any cycle boundary.

The PIC24F has a vectored exception scheme with up to 8 sources of non-maskable traps and

interrupt sources. Each interrupt source can be assigned to one of seven priority levels.

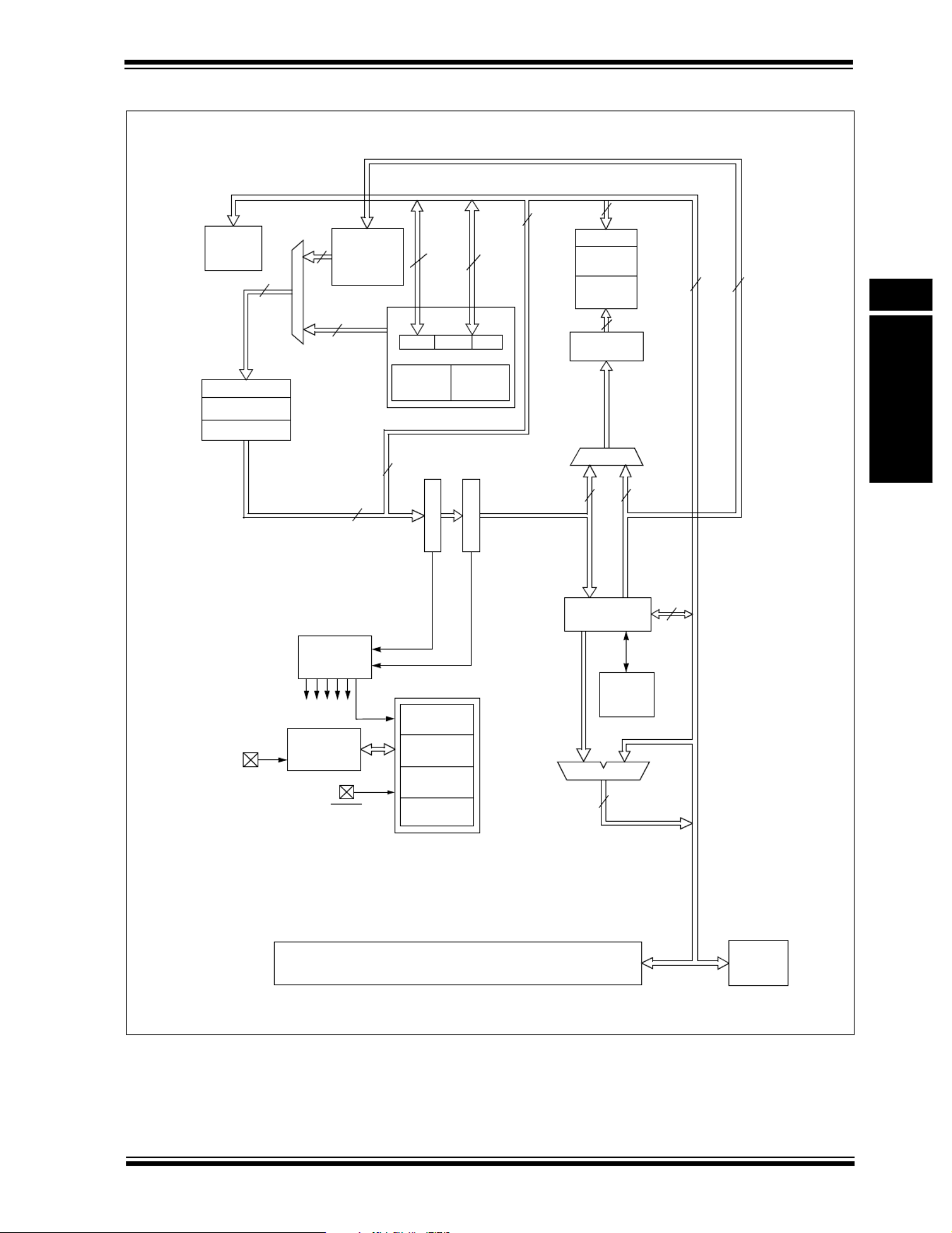

A block diagram of the CPU is shown in Figure 2-1.

© 2006 Microchip Technology Inc. Advance Information DS39703A-page 2-3

Section 2. CPU

CPU

2

Figure 2-1: PIC24F CPU Core Block Diagram

Power-up

Timer

Oscillator

Start-up Timer

POR/BOR

Reset

Watchdog

Timer

Instruction

Decode &

Control

OSC1/CLKI

MCLR

Timing

Generation

16

PCH PCL

16

Program Counter

16-Bit ALU

23

23

24

23

Data Bus

IR

PCU

16

16 x 16

W Reg Array

ROM Latch

16

EA MUX

RAGU

WAGU

16

16

16

16

8

Interrupt

Controller PSV & Table

Data Access

Control Block

Stack

Control

Logic

Loop

Control

Logic

Data Latch

Data

RAM

Address

Latch

Control Signals

to Various Blocks

Address Latch

Program Memory

Data Latch

I/O Ports

16

16

Address Bus

16

Literal Data

Peripherals

Multiplier

and Divide

Support

Specyfikacje produktu

| Marka: | Microchip |

| Kategoria: | Niesklasyfikowane |

| Model: | PIC24F32KA304 |

Potrzebujesz pomocy?

Jeśli potrzebujesz pomocy z Microchip PIC24F32KA304, zadaj pytanie poniżej, a inni użytkownicy Ci odpowiedzą

Instrukcje Niesklasyfikowane Microchip

15 Stycznia 2025

15 Stycznia 2025

15 Stycznia 2025

15 Stycznia 2025

15 Stycznia 2025

15 Stycznia 2025

15 Stycznia 2025

15 Stycznia 2025

15 Stycznia 2025

15 Stycznia 2025

Instrukcje Niesklasyfikowane

- Niesklasyfikowane Sony

- Niesklasyfikowane Bauknecht

- Niesklasyfikowane Yamaha

- Niesklasyfikowane Ikea

- Niesklasyfikowane Hoshizaki

- Niesklasyfikowane Samsung

- Niesklasyfikowane Tesy

- Niesklasyfikowane Kindercraft

- Niesklasyfikowane PeakTech

- Niesklasyfikowane Bertazzoni

- Niesklasyfikowane Electrolux

- Niesklasyfikowane Gamdias

- Niesklasyfikowane Tenda

- Niesklasyfikowane AEG

- Niesklasyfikowane Fellowes

- Niesklasyfikowane Balay

- Niesklasyfikowane Leica

- Niesklasyfikowane Beko

- Niesklasyfikowane Teka

- Niesklasyfikowane Sven

- Niesklasyfikowane ChamSys

- Niesklasyfikowane LG

- Niesklasyfikowane Worx

- Niesklasyfikowane Küppersbusch

- Niesklasyfikowane Smeg

- Niesklasyfikowane Motorola

- Niesklasyfikowane Götze & Jensen

- Niesklasyfikowane Dreame

- Niesklasyfikowane Beurer

- Niesklasyfikowane Peugeot

- Niesklasyfikowane Stabo

- Niesklasyfikowane Logitech

- Niesklasyfikowane Gram

- Niesklasyfikowane Sanitas

- Niesklasyfikowane Spektrum

- Niesklasyfikowane Caso

- Niesklasyfikowane Amica

- Niesklasyfikowane Xiaomi

- Niesklasyfikowane Gorenje

- Niesklasyfikowane Etna

- Niesklasyfikowane Joy-It

- Niesklasyfikowane LERAN

- Niesklasyfikowane Lego

- Niesklasyfikowane SHX

- Niesklasyfikowane President

- Niesklasyfikowane MyPhone

- Niesklasyfikowane Sharp

- Niesklasyfikowane BeamZ

- Niesklasyfikowane Huawei

- Niesklasyfikowane Supermicro

- Niesklasyfikowane TCL

- Niesklasyfikowane Braun

- Niesklasyfikowane Russell Hobbs

- Niesklasyfikowane Pioneer

- Niesklasyfikowane Statron

- Niesklasyfikowane Lenovo

- Niesklasyfikowane Tefal

- Niesklasyfikowane Honda

- Niesklasyfikowane TP-Link

- Niesklasyfikowane Voltcraft

- Niesklasyfikowane Milwaukee

- Niesklasyfikowane Philips

- Niesklasyfikowane Livoo

- Niesklasyfikowane Plantronics

- Niesklasyfikowane SilverCrest

- Niesklasyfikowane Endress

- Niesklasyfikowane Dometic

- Niesklasyfikowane Gigabyte

- Niesklasyfikowane Acer

- Niesklasyfikowane Realme

- Niesklasyfikowane Ultimate Speed

- Niesklasyfikowane Technics

- Niesklasyfikowane Stihl

- Niesklasyfikowane Bosch

- Niesklasyfikowane Yato

- Niesklasyfikowane Xblitz

- Niesklasyfikowane Dash

- Niesklasyfikowane Epson

- Niesklasyfikowane JBL

- Niesklasyfikowane Parkside

- Niesklasyfikowane Hikvision

- Niesklasyfikowane Candy

- Niesklasyfikowane GW Instek

- Niesklasyfikowane Maxi-Cosi

- Niesklasyfikowane Onkyo

- Niesklasyfikowane Volkswagen

- Niesklasyfikowane Whirlpool

- Niesklasyfikowane Grillmeister

- Niesklasyfikowane IPGARD

- Niesklasyfikowane Lionelo

- Niesklasyfikowane Fujitsu

- Niesklasyfikowane Ferroli

- Niesklasyfikowane Edision

- Niesklasyfikowane Global

- Niesklasyfikowane Thule

- Niesklasyfikowane Roland

- Niesklasyfikowane Cramer

- Niesklasyfikowane Miele

- Niesklasyfikowane HyperX

- Niesklasyfikowane Stiga

- Niesklasyfikowane Easy Home

- Niesklasyfikowane Hacienda

- Niesklasyfikowane LC-Power

- Niesklasyfikowane Waterco

- Niesklasyfikowane Geemarc

- Niesklasyfikowane Nokia

- Niesklasyfikowane Scott

- Niesklasyfikowane Brentwood

- Niesklasyfikowane Nobo

- Niesklasyfikowane Midea

- Niesklasyfikowane Toolcraft

- Niesklasyfikowane Axkid

- Niesklasyfikowane KEF

- Niesklasyfikowane Festool

- Niesklasyfikowane Kärcher

- Niesklasyfikowane Bose

- Niesklasyfikowane Severin

- Niesklasyfikowane Hisense

- Niesklasyfikowane Berg

- Niesklasyfikowane Infiniton

- Niesklasyfikowane EZVIZ

- Niesklasyfikowane Conceptronic

- Niesklasyfikowane Singer

- Niesklasyfikowane Panasonic

- Niesklasyfikowane StarTech.com

- Niesklasyfikowane Promethean

- Niesklasyfikowane Bavaria By Einhell

- Niesklasyfikowane Theben

- Niesklasyfikowane Klipsch

- Niesklasyfikowane Muse

- Niesklasyfikowane Liebherr

- Niesklasyfikowane Canon

- Niesklasyfikowane Mio

- Niesklasyfikowane Crestron

- Niesklasyfikowane Withings

- Niesklasyfikowane Bestway

- Niesklasyfikowane Viewsonic

- Niesklasyfikowane Behringer

- Niesklasyfikowane Asus

- Niesklasyfikowane Nedis

- Niesklasyfikowane Stanley

- Niesklasyfikowane Nexa

- Niesklasyfikowane Jura

- Niesklasyfikowane AG Neovo

- Niesklasyfikowane Be Cool

- Niesklasyfikowane Allen & Heath

- Niesklasyfikowane Enphase

- Niesklasyfikowane Rossmax

- Niesklasyfikowane IK Multimedia

- Niesklasyfikowane Reolink

- Niesklasyfikowane American DJ

- Niesklasyfikowane Medion

- Niesklasyfikowane Boss

- Niesklasyfikowane Black & Decker

- Niesklasyfikowane OK

- Niesklasyfikowane Lenco

- Niesklasyfikowane TRENDnet

- Niesklasyfikowane Audioline

- Niesklasyfikowane Polar

- Niesklasyfikowane Max Pro

- Niesklasyfikowane Scheppach

- Niesklasyfikowane Fujifilm

- Niesklasyfikowane Proxxon

- Niesklasyfikowane Adler

- Niesklasyfikowane Bluetti

- Niesklasyfikowane BaByliss

- Niesklasyfikowane Marquant

- Niesklasyfikowane Subaru

- Niesklasyfikowane MSI

- Niesklasyfikowane Ford

- Niesklasyfikowane Hoover

- Niesklasyfikowane Toshiba

- Niesklasyfikowane Tesla

- Niesklasyfikowane Deditec

- Niesklasyfikowane Westinghouse

- Niesklasyfikowane D-Link

- Niesklasyfikowane Rinnai

- Niesklasyfikowane Majestic

- Niesklasyfikowane Hendi

- Niesklasyfikowane Quigg

- Niesklasyfikowane Jensen

- Niesklasyfikowane August

- Niesklasyfikowane Niceboy

- Niesklasyfikowane Maytag

- Niesklasyfikowane Hazet

- Niesklasyfikowane Bluebird

- Niesklasyfikowane Vertiv

- Niesklasyfikowane Yealink

- Niesklasyfikowane Domo

- Niesklasyfikowane Conair

- Niesklasyfikowane GE

- Niesklasyfikowane ILive

- Niesklasyfikowane Ardes

- Niesklasyfikowane Taurus

- Niesklasyfikowane VitalMaxx

- Niesklasyfikowane RIKON

- Niesklasyfikowane Ring

- Niesklasyfikowane Orbegozo

- Niesklasyfikowane Native Instruments

- Niesklasyfikowane Garmin

- Niesklasyfikowane Blaupunkt

- Niesklasyfikowane Profoon

- Niesklasyfikowane Brandt

- Niesklasyfikowane Vivax

- Niesklasyfikowane ATen

- Niesklasyfikowane IOptron

- Niesklasyfikowane Grizzly

- Niesklasyfikowane Siemens

- Niesklasyfikowane Teac

- Niesklasyfikowane Speed-Link

- Niesklasyfikowane Gardena

- Niesklasyfikowane Casio

- Niesklasyfikowane Iiyama

- Niesklasyfikowane Lincoln Electric

- Niesklasyfikowane BRITA

- Niesklasyfikowane Metra

- Niesklasyfikowane Thrustmaster

- Niesklasyfikowane Volvo

- Niesklasyfikowane Evolveo

- Niesklasyfikowane Stadler Form

- Niesklasyfikowane Ambiano

- Niesklasyfikowane DeWalt

- Niesklasyfikowane Bbf

- Niesklasyfikowane Danby

- Niesklasyfikowane Martin Logan

- Niesklasyfikowane Dual

- Niesklasyfikowane Einhell

- Niesklasyfikowane Grundig

- Niesklasyfikowane APC

- Niesklasyfikowane Hegel

- Niesklasyfikowane Alcatel

- Niesklasyfikowane Kiloview

- Niesklasyfikowane Suzuki

- Niesklasyfikowane Haier

- Niesklasyfikowane Sigma

- Niesklasyfikowane Homedics

- Niesklasyfikowane Remington

- Niesklasyfikowane Eberle

- Niesklasyfikowane HP

- Niesklasyfikowane KKT Kolbe

- Niesklasyfikowane Cylinda

- Niesklasyfikowane Teltonika

- Niesklasyfikowane S.M.S.L

- Niesklasyfikowane Genesis

- Niesklasyfikowane Jocel

- Niesklasyfikowane Soundmaster

- Niesklasyfikowane Prixton

- Niesklasyfikowane Hyundai

- Niesklasyfikowane Silverline

- Niesklasyfikowane Blomberg

- Niesklasyfikowane Bimar

- Niesklasyfikowane Line 6

- Niesklasyfikowane Rowenta

- Niesklasyfikowane Brother

- Niesklasyfikowane Mesko

- Niesklasyfikowane Master

- Niesklasyfikowane Husqvarna

- Niesklasyfikowane Honeywell

- Niesklasyfikowane DAP-Audio

- Niesklasyfikowane Creative

- Niesklasyfikowane Concept

- Niesklasyfikowane Joie

- Niesklasyfikowane Manhattan

- Niesklasyfikowane Chauvet

- Niesklasyfikowane Strong

- Niesklasyfikowane Cybex

- Niesklasyfikowane Honor

- Niesklasyfikowane Heritage Audio

- Niesklasyfikowane Fisher & Paykel

- Niesklasyfikowane Cotek

- Niesklasyfikowane Tripp Lite

- Niesklasyfikowane Shure

- Niesklasyfikowane EWON

- Niesklasyfikowane ECG

- Niesklasyfikowane IRobot

- Niesklasyfikowane Indesit

- Niesklasyfikowane Amazfit

- Niesklasyfikowane Steinel

- Niesklasyfikowane Makita

- Niesklasyfikowane Ilve

- Niesklasyfikowane Mikrotik

- Niesklasyfikowane Hecht

- Niesklasyfikowane Denon

- Niesklasyfikowane Akasa

- Niesklasyfikowane Unold

- Niesklasyfikowane Swann

- Niesklasyfikowane Krontaler

- Niesklasyfikowane Truma

- Niesklasyfikowane Kwikset

- Niesklasyfikowane Mercury

- Niesklasyfikowane Empress Effects

- Niesklasyfikowane Carel

- Niesklasyfikowane Petzl

- Niesklasyfikowane Nikon

- Niesklasyfikowane Shimano

- Niesklasyfikowane Viking

- Niesklasyfikowane Antari

- Niesklasyfikowane Medela

- Niesklasyfikowane Block

- Niesklasyfikowane Rapid

- Niesklasyfikowane Ozito

- Niesklasyfikowane Primus

- Niesklasyfikowane Kodak

- Niesklasyfikowane Phoenix Gold

- Niesklasyfikowane Nodor

- Niesklasyfikowane Forza

- Niesklasyfikowane CATA

- Niesklasyfikowane Testo

- Niesklasyfikowane HeiTech

- Niesklasyfikowane Audac

- Niesklasyfikowane Cisco

- Niesklasyfikowane Baby Brezza

- Niesklasyfikowane Primera

- Niesklasyfikowane SBS

- Niesklasyfikowane Draper

- Niesklasyfikowane Cambridge

- Niesklasyfikowane Fuxtec

- Niesklasyfikowane Smart

- Niesklasyfikowane ORNO

- Niesklasyfikowane Fiap

- Niesklasyfikowane Cooler Master

- Niesklasyfikowane Sanus

- Niesklasyfikowane TFA

- Niesklasyfikowane Dyson

- Niesklasyfikowane Chauvin Arnoux

- Niesklasyfikowane Broan

- Niesklasyfikowane Hotpoint

- Niesklasyfikowane Kenwood

- Niesklasyfikowane Scosche

- Niesklasyfikowane Icy Box

- Niesklasyfikowane Sungrow

- Niesklasyfikowane NuPrime

- Niesklasyfikowane Polk

- Niesklasyfikowane Hasbro

- Niesklasyfikowane V-Zug

- Niesklasyfikowane Moxa

- Niesklasyfikowane Deye

- Niesklasyfikowane Trisa

- Niesklasyfikowane DJI

- Niesklasyfikowane RYOBI

- Niesklasyfikowane Synology

- Niesklasyfikowane Godex

- Niesklasyfikowane Kugoo

- Niesklasyfikowane Alpine

- Niesklasyfikowane Wolf Garten

- Niesklasyfikowane Natec

- Niesklasyfikowane Knog

- Niesklasyfikowane Zenit

- Niesklasyfikowane Gembird

- Niesklasyfikowane Scala

- Niesklasyfikowane ZTE

- Niesklasyfikowane Godox

- Niesklasyfikowane Uni-T

- Niesklasyfikowane Røde

- Niesklasyfikowane Ariston Thermo

- Niesklasyfikowane Zelmer

- Niesklasyfikowane Vango

- Niesklasyfikowane Hammersmith

- Niesklasyfikowane Chicco

- Niesklasyfikowane Mestic

- Niesklasyfikowane My Wall

- Niesklasyfikowane Chamberlain

- Niesklasyfikowane Dynaudio

- Niesklasyfikowane Paradigm

- Niesklasyfikowane Paladin

- Niesklasyfikowane Spin Master

- Niesklasyfikowane Lindy

- Niesklasyfikowane Olivetti

- Niesklasyfikowane PKM

- Niesklasyfikowane Ninja

- Niesklasyfikowane Medisana

- Niesklasyfikowane MaxCom

- Niesklasyfikowane Minox

- Niesklasyfikowane Cuisinart

- Niesklasyfikowane Zebra

- Niesklasyfikowane Bang & Olufsen

- Niesklasyfikowane Wilfa

- Niesklasyfikowane DSC

- Niesklasyfikowane Deltaco

- Niesklasyfikowane Cobra

- Niesklasyfikowane Flex

- Niesklasyfikowane JVC

- Niesklasyfikowane ZyXEL

- Niesklasyfikowane Auriol

- Niesklasyfikowane Konig & Meyer

- Niesklasyfikowane Trust

- Niesklasyfikowane V7

- Niesklasyfikowane Thor

- Niesklasyfikowane LogiLink

- Niesklasyfikowane Amana

- Niesklasyfikowane Stokke

- Niesklasyfikowane Memphis Audio

- Niesklasyfikowane Intergas

- Niesklasyfikowane Sandisk

- Niesklasyfikowane Grohe

- Niesklasyfikowane Dell

- Niesklasyfikowane Dacor

- Niesklasyfikowane Polaris

- Niesklasyfikowane Fitbit

- Niesklasyfikowane Axor

- Niesklasyfikowane GLORIA

- Niesklasyfikowane Yard Force

- Niesklasyfikowane IFM

- Niesklasyfikowane Spelsberg

- Niesklasyfikowane Hotpoint Ariston

- Niesklasyfikowane Ctek

- Niesklasyfikowane Krups

- Niesklasyfikowane Datapath

- Niesklasyfikowane Furrion

- Niesklasyfikowane Bialetti

- Niesklasyfikowane Silk'n

- Niesklasyfikowane Bomann

- Niesklasyfikowane U-Line

- Niesklasyfikowane Linksys

- Niesklasyfikowane Clean Air Optima

- Niesklasyfikowane Moulinex

- Niesklasyfikowane Teesa

- Niesklasyfikowane Cleanmaxx

- Niesklasyfikowane Ursus Trotter

- Niesklasyfikowane Ultimate

- Niesklasyfikowane Aprilia

- Niesklasyfikowane PS Audio

- Niesklasyfikowane PowerXL

- Niesklasyfikowane Jamo

- Niesklasyfikowane DEDRA

- Niesklasyfikowane Corsair

- Niesklasyfikowane Emerio

- Niesklasyfikowane Owon

- Niesklasyfikowane Focusrite

- Niesklasyfikowane Wood's

- Niesklasyfikowane Baumr-AG

- Niesklasyfikowane Nuna

- Niesklasyfikowane Google

- Niesklasyfikowane Create

- Niesklasyfikowane Rega

- Niesklasyfikowane Intex

- Niesklasyfikowane Biltema

- Niesklasyfikowane Oricom

- Niesklasyfikowane B.E.G.

- Niesklasyfikowane Crane

- Niesklasyfikowane H.Koenig

- Niesklasyfikowane InAlto

- Niesklasyfikowane CMI

- Niesklasyfikowane Hilti

- Niesklasyfikowane Eastron

- Niesklasyfikowane Meireles

- Niesklasyfikowane Revitive

- Niesklasyfikowane Digitus

- Niesklasyfikowane Salewa

- Niesklasyfikowane Fimi

- Niesklasyfikowane Oppo

- Niesklasyfikowane Cateye

- Niesklasyfikowane Thinkware

- Niesklasyfikowane Alesis

- Niesklasyfikowane Lowrance

- Niesklasyfikowane Tanita

- Niesklasyfikowane Anybus

- Niesklasyfikowane Melissa

- Niesklasyfikowane TechniSat

- Niesklasyfikowane Auna

- Niesklasyfikowane Vimar

- Niesklasyfikowane V-TAC

- Niesklasyfikowane Dahua Technology

- Niesklasyfikowane Schneider

- Niesklasyfikowane Deutz

- Niesklasyfikowane SABO

- Niesklasyfikowane Ledlenser

- Niesklasyfikowane Beper

- Niesklasyfikowane Infomir

- Niesklasyfikowane Eurolite

- Niesklasyfikowane Kyocera

- Niesklasyfikowane LD Systems

- Niesklasyfikowane Techno Line

- Niesklasyfikowane SuperTooth

- Niesklasyfikowane Foppapedretti

- Niesklasyfikowane Foreo

- Niesklasyfikowane Daikin

- Niesklasyfikowane Kospel

- Niesklasyfikowane EVOline

- Niesklasyfikowane Kubota

- Niesklasyfikowane Thetford

- Niesklasyfikowane TrueLife

- Niesklasyfikowane Eufy

- Niesklasyfikowane Stirling

- Niesklasyfikowane Ricoh

- Niesklasyfikowane Krüger&Matz

- Niesklasyfikowane TOGU

- Niesklasyfikowane SMART Technologies

- Niesklasyfikowane Mad Dog

- Niesklasyfikowane NZXT

- Niesklasyfikowane Audioengine

- Niesklasyfikowane Hozelock

- Niesklasyfikowane Playmobil

- Niesklasyfikowane MPM

- Niesklasyfikowane OneConcept

- Niesklasyfikowane Recaro

- Niesklasyfikowane Hori

- Niesklasyfikowane CDA

- Niesklasyfikowane Emos

- Niesklasyfikowane Sabrent

- Niesklasyfikowane AVMATRIX

- Niesklasyfikowane IMC Toys

- Niesklasyfikowane Philco

- Niesklasyfikowane Neff

- Niesklasyfikowane Seiko

- Niesklasyfikowane Renkforce

- Niesklasyfikowane Rollei

- Niesklasyfikowane Corbero

- Niesklasyfikowane Morphy Richards

- Niesklasyfikowane Zanussi

- Niesklasyfikowane Sekonic

- Niesklasyfikowane Hensel

- Niesklasyfikowane Sonel

- Niesklasyfikowane Pure

- Niesklasyfikowane NightStick

- Niesklasyfikowane Ravanson

- Niesklasyfikowane Crivit

- Niesklasyfikowane Marshall

- Niesklasyfikowane Zenec

- Niesklasyfikowane Audiotec Fischer

- Niesklasyfikowane Osram

- Niesklasyfikowane BaseTech

- Niesklasyfikowane Thermex

- Niesklasyfikowane AXA

- Niesklasyfikowane Traxxas

- Niesklasyfikowane Viessmann

- Niesklasyfikowane Perel

- Niesklasyfikowane Janitza

- Niesklasyfikowane Wagner

- Niesklasyfikowane Salta

- Niesklasyfikowane Fagor

- Niesklasyfikowane Redmond

- Niesklasyfikowane Sena

- Niesklasyfikowane Koenic

- Niesklasyfikowane Graco

- Niesklasyfikowane Trotec

- Niesklasyfikowane Autel

- Niesklasyfikowane Somfy

- Niesklasyfikowane Everdure

- Niesklasyfikowane Uniden

- Niesklasyfikowane Adder

- Niesklasyfikowane Ansmann

- Niesklasyfikowane Clarion

- Niesklasyfikowane Wacom

- Niesklasyfikowane Omron

- Niesklasyfikowane Netgear

- Niesklasyfikowane Cellular Line

- Niesklasyfikowane Thomson

- Niesklasyfikowane DiO

- Niesklasyfikowane Pro-Ject

- Niesklasyfikowane Dremel

- Niesklasyfikowane Texas Instruments

- Niesklasyfikowane Lastolite

- Niesklasyfikowane AVM

- Niesklasyfikowane La Crosse Technology

- Niesklasyfikowane Growatt

- Niesklasyfikowane Velux

- Niesklasyfikowane Izzy

- Niesklasyfikowane Fresh 'n Rebel

- Niesklasyfikowane Little Tikes

- Niesklasyfikowane Chipolino

- Niesklasyfikowane Velleman

- Niesklasyfikowane Ferguson

- Niesklasyfikowane BT

- Niesklasyfikowane Meec Tools

- Niesklasyfikowane Fusion

- Niesklasyfikowane BOYA

- Niesklasyfikowane WMF

- Niesklasyfikowane Korg

- Niesklasyfikowane ProfiCook

- Niesklasyfikowane Homematic IP

- Niesklasyfikowane Neumann

- Niesklasyfikowane DataVideo

- Niesklasyfikowane AL-KO

- Niesklasyfikowane One For All

- Niesklasyfikowane Klarstein

- Niesklasyfikowane BEEM

- Niesklasyfikowane Wharfedale

- Niesklasyfikowane Safety 1st

- Niesklasyfikowane Polti

- Niesklasyfikowane Totolink

- Niesklasyfikowane Victor Technology

- Niesklasyfikowane Danfoss

- Niesklasyfikowane JYSK

- Niesklasyfikowane Coyote

- Niesklasyfikowane Intertechno

- Niesklasyfikowane Magnat

- Niesklasyfikowane Black Box

- Niesklasyfikowane Lowepro

- Niesklasyfikowane Güde

- Niesklasyfikowane Arendo

- Niesklasyfikowane Revamp

- Niesklasyfikowane DreamGEAR

- Niesklasyfikowane Witt

- Niesklasyfikowane Victron Energy

- Niesklasyfikowane Delta Dore

- Niesklasyfikowane E-ast

- Niesklasyfikowane Hobby

- Niesklasyfikowane Manta

- Niesklasyfikowane Pyle

- Niesklasyfikowane CTA Digital

- Niesklasyfikowane Segway

- Niesklasyfikowane Gem Toys

- Niesklasyfikowane Texas

- Niesklasyfikowane Apple

- Niesklasyfikowane ELAC

- Niesklasyfikowane Lancom

- Niesklasyfikowane Adviti

- Niesklasyfikowane Crimson

- Niesklasyfikowane Dymo

- Niesklasyfikowane ATIKA

- Niesklasyfikowane Hauck

- Niesklasyfikowane Bikemate

- Niesklasyfikowane Zoom

- Niesklasyfikowane Iogear

- Niesklasyfikowane Cardo

- Niesklasyfikowane Panduit

- Niesklasyfikowane Intellinet

- Niesklasyfikowane Datalogic

- Niesklasyfikowane NGS

- Niesklasyfikowane CRUX

- Niesklasyfikowane Vaillant

- Niesklasyfikowane Beautifly

- Niesklasyfikowane Newline

- Niesklasyfikowane Bavaria

- Niesklasyfikowane Devolo

- Niesklasyfikowane Juwel

- Niesklasyfikowane Biostar

- Niesklasyfikowane Cecotec

- Niesklasyfikowane Artusi

- Niesklasyfikowane Vileda

- Niesklasyfikowane Dirt Devil

- Niesklasyfikowane Midland

- Niesklasyfikowane Marantz

- Niesklasyfikowane KitchenAid

- Niesklasyfikowane MARTOR

- Niesklasyfikowane AFK

- Niesklasyfikowane Waeco

- Niesklasyfikowane AOC

- Niesklasyfikowane Cougar

- Niesklasyfikowane Monster

- Niesklasyfikowane Sennheiser

- Niesklasyfikowane JANDY

- Niesklasyfikowane Esoteric

- Niesklasyfikowane Roidmi

- Niesklasyfikowane Jabra

- Niesklasyfikowane Chord

- Niesklasyfikowane Zipper

- Niesklasyfikowane Vivotek

- Niesklasyfikowane Eta

- Niesklasyfikowane Mount-It!

- Niesklasyfikowane Kingston

- Niesklasyfikowane Camry

- Niesklasyfikowane Vtech

- Niesklasyfikowane Steba

- Niesklasyfikowane Werma

- Niesklasyfikowane Perixx

- Niesklasyfikowane Peerless-AV

- Niesklasyfikowane Speco Technologies

- Niesklasyfikowane Medeli

- Niesklasyfikowane Suunto

- Niesklasyfikowane Showtec

- Niesklasyfikowane Weber

- Niesklasyfikowane Heckler Design

- Niesklasyfikowane Lenoxx

- Niesklasyfikowane Keurig

- Niesklasyfikowane Grundfos

- Niesklasyfikowane Bowers & Wilkins

- Niesklasyfikowane Samson

- Niesklasyfikowane EtiamPro

- Niesklasyfikowane EA Elektro Automatik

- Niesklasyfikowane Tineco

- Niesklasyfikowane Imperial

- Niesklasyfikowane Emporia

- Niesklasyfikowane Helios

- Niesklasyfikowane Scarlett

- Niesklasyfikowane SodaStream

- Niesklasyfikowane Microlife

- Niesklasyfikowane PreSonus

- Niesklasyfikowane Mercusys

- Niesklasyfikowane Koss

- Niesklasyfikowane Monitor Audio

- Niesklasyfikowane Audio Pro

- Niesklasyfikowane I-TEC

- Niesklasyfikowane Weston

- Niesklasyfikowane ARRI

- Niesklasyfikowane ResMed

- Niesklasyfikowane Blackstar

- Niesklasyfikowane NACON

- Niesklasyfikowane Gossen Metrawatt

- Niesklasyfikowane Sôlt

- Niesklasyfikowane Mafell

- Niesklasyfikowane Eden

- Niesklasyfikowane Fosi Audio

- Niesklasyfikowane TC Electronic

- Niesklasyfikowane GUTFELS

- Niesklasyfikowane Shelly

- Niesklasyfikowane Revox

- Niesklasyfikowane Fluke

- Niesklasyfikowane Nevir

- Niesklasyfikowane Kindermann

- Niesklasyfikowane Megger

- Niesklasyfikowane Ewent

- Niesklasyfikowane HyperIce

- Niesklasyfikowane Olympus

- Niesklasyfikowane Navitel

- Niesklasyfikowane Greisinger

- Niesklasyfikowane Draytek

- Niesklasyfikowane TriStar

- Niesklasyfikowane Ibiza Sound

- Niesklasyfikowane MTD

- Niesklasyfikowane Oliveri

- Niesklasyfikowane Vonyx

- Niesklasyfikowane Musical Fidelity

- Niesklasyfikowane Master Lock

- Niesklasyfikowane Numatic

- Niesklasyfikowane Bogen

- Niesklasyfikowane Landmann

- Niesklasyfikowane Pulsar

- Niesklasyfikowane PATLITE

- Niesklasyfikowane Exquisit

- Niesklasyfikowane Bartscher

- Niesklasyfikowane Phanteks

- Niesklasyfikowane First Austria

- Niesklasyfikowane Alto

- Niesklasyfikowane Hestan

- Niesklasyfikowane Fiskars

- Niesklasyfikowane Gastroback

- Niesklasyfikowane GYS

- Niesklasyfikowane Mitsubishi

- Niesklasyfikowane Privileg

- Niesklasyfikowane Avaya

- Niesklasyfikowane Edimax

- Niesklasyfikowane Naim

- Niesklasyfikowane Razer

- Niesklasyfikowane Grothe

- Niesklasyfikowane Dimplex

- Niesklasyfikowane Falmec

- Niesklasyfikowane National Geographic

- Niesklasyfikowane Florabest

- Niesklasyfikowane Harvia

- Niesklasyfikowane Baxi

- Niesklasyfikowane BeSafe

- Niesklasyfikowane ADATA

- Niesklasyfikowane Kidde

- Niesklasyfikowane Chief

- Niesklasyfikowane 4ms

- Niesklasyfikowane Peavey

- Niesklasyfikowane IVT

- Niesklasyfikowane GoClever

- Niesklasyfikowane Sunding

- Niesklasyfikowane Baby Lock

- Niesklasyfikowane Dehner

- Niesklasyfikowane Bryton

- Niesklasyfikowane Weidmüller

- Niesklasyfikowane BENNING

- Niesklasyfikowane ION

- Niesklasyfikowane Camille Bauer

- Niesklasyfikowane Huion

- Niesklasyfikowane Arçelik

- Niesklasyfikowane ART

- Niesklasyfikowane First Alert

- Niesklasyfikowane Hanseatic

- Niesklasyfikowane Assa Abloy

- Niesklasyfikowane NAD

- Niesklasyfikowane Solo

- Niesklasyfikowane Continental Edison

- Niesklasyfikowane RCF

- Niesklasyfikowane Topmove

- Niesklasyfikowane Delta

- Niesklasyfikowane Kerbl

- Niesklasyfikowane Bifinett

- Niesklasyfikowane SEH

- Niesklasyfikowane Zhiyun

- Niesklasyfikowane Gree

- Niesklasyfikowane Fluval

- Niesklasyfikowane Bissell

- Niesklasyfikowane AirLive

- Niesklasyfikowane Harman Kardon

- Niesklasyfikowane Rolls

- Niesklasyfikowane Audio-Technica

- Niesklasyfikowane Maginon

- Niesklasyfikowane EnGenius

- Niesklasyfikowane SPC

- Niesklasyfikowane Atag

- Niesklasyfikowane Babymoov

- Niesklasyfikowane Rosieres

- Niesklasyfikowane Franke

- Niesklasyfikowane Planet

- Niesklasyfikowane Intermec

- Niesklasyfikowane Dahle

- Niesklasyfikowane XGIMI

- Niesklasyfikowane Adidas

- Niesklasyfikowane GoGen

- Niesklasyfikowane Intenso

- Niesklasyfikowane DCG

- Niesklasyfikowane Accu-Chek

- Niesklasyfikowane Genie

- Niesklasyfikowane TC Helicon

- Niesklasyfikowane RCBS

- Niesklasyfikowane Peg Perego

- Niesklasyfikowane NEC

- Niesklasyfikowane Rexel

- Niesklasyfikowane Brandson

- Niesklasyfikowane Soundcraft

- Niesklasyfikowane Beautiful

- Niesklasyfikowane Metrix

- Niesklasyfikowane Parrot

- Niesklasyfikowane Antec

- Niesklasyfikowane Vornado

- Niesklasyfikowane Polaroid

- Niesklasyfikowane Rocktrail

- Niesklasyfikowane Prestigio

- Niesklasyfikowane Blustream

- Niesklasyfikowane Aiwa

- Niesklasyfikowane G3 Ferrari

- Niesklasyfikowane Ooni

- Niesklasyfikowane JL Audio

- Niesklasyfikowane LevelOne

- Niesklasyfikowane Omega Altise

- Niesklasyfikowane Konica Minolta

- Niesklasyfikowane Bugaboo

- Niesklasyfikowane AKAI

- Niesklasyfikowane Tunturi

- Niesklasyfikowane Razor

- Niesklasyfikowane Digi

- Niesklasyfikowane JLab

- Niesklasyfikowane Maglite

- Niesklasyfikowane Mobicool

- Niesklasyfikowane Axis

- Niesklasyfikowane Sanyo

- Niesklasyfikowane ICOM

- Niesklasyfikowane Vivolink

- Niesklasyfikowane Life Fitness

- Niesklasyfikowane Red Digital Cinema

- Niesklasyfikowane Westfalia

- Niesklasyfikowane Hamilton Beach

- Niesklasyfikowane Majority

- Niesklasyfikowane Elvid

- Niesklasyfikowane Hayward

- Niesklasyfikowane Neumärker

- Niesklasyfikowane REL Acoustics

- Niesklasyfikowane Flaem

- Niesklasyfikowane Gourmetmaxx

- Niesklasyfikowane Rigol

- Niesklasyfikowane Bixolon

- Niesklasyfikowane Ergotools Pattfield

- Niesklasyfikowane Hoymiles

- Niesklasyfikowane Teufel

- Niesklasyfikowane Novy

- Niesklasyfikowane Suevia

- Niesklasyfikowane Remko

- Niesklasyfikowane Hartke

- Niesklasyfikowane Clatronic

- Niesklasyfikowane BabyBjörn

- Niesklasyfikowane Healthy Choice

- Niesklasyfikowane Tronic

- Niesklasyfikowane Klark Teknik

- Niesklasyfikowane Dali

- Niesklasyfikowane Vision

- Niesklasyfikowane Telefunken

- Niesklasyfikowane NEO Tools

- Niesklasyfikowane Oregon Scientific

- Niesklasyfikowane Lorex

- Niesklasyfikowane Eventide

- Niesklasyfikowane Optoma

- Niesklasyfikowane Melitta

- Niesklasyfikowane Rommer

- Niesklasyfikowane Proel

- Niesklasyfikowane Calor

- Niesklasyfikowane Inventum

- Niesklasyfikowane SVAN

- Niesklasyfikowane Ariete

- Niesklasyfikowane Flame

- Niesklasyfikowane Hifonics

- Niesklasyfikowane Vogel's

- Niesklasyfikowane Heidemann

- Niesklasyfikowane Fuzzix

- Niesklasyfikowane Focal

- Niesklasyfikowane OnePlus

- Niesklasyfikowane Tepro

- Niesklasyfikowane Bernina

- Niesklasyfikowane Asrock

- Niesklasyfikowane LiftMaster

- Niesklasyfikowane Taga Harmony

- Niesklasyfikowane Graef

- Niesklasyfikowane Viper

- Niesklasyfikowane Napoleon

- Niesklasyfikowane Audix

- Niesklasyfikowane Milesight

- Niesklasyfikowane DBX

- Niesklasyfikowane Princess

- Niesklasyfikowane Baby Jogger

- Niesklasyfikowane Kicker

- Niesklasyfikowane Amazon

- Niesklasyfikowane Carson

- Niesklasyfikowane Doepfer

- Niesklasyfikowane TDE Instruments

- Niesklasyfikowane Innoliving

- Niesklasyfikowane Aluratek

- Niesklasyfikowane Abus

- Niesklasyfikowane Thorens

- Niesklasyfikowane Bresser

- Niesklasyfikowane Sunbeam

- Niesklasyfikowane Rocstor

- Niesklasyfikowane Reebok

- Niesklasyfikowane Omnitronic

- Niesklasyfikowane Livarno Lux

- Niesklasyfikowane Solac

- Niesklasyfikowane Valco Baby

- Niesklasyfikowane Elro

- Niesklasyfikowane Olympia

- Niesklasyfikowane Jay-Tech

- Niesklasyfikowane Novis

- Niesklasyfikowane Hama

- Niesklasyfikowane Mackie

- Niesklasyfikowane Juki

- Niesklasyfikowane Shokz

- Niesklasyfikowane Microsoft

- Niesklasyfikowane Marmitek

- Niesklasyfikowane Busch + Müller

- Niesklasyfikowane Eltako

- Niesklasyfikowane Heller

- Niesklasyfikowane Palmer

- Niesklasyfikowane Sanitaire

- Niesklasyfikowane FiiO

- Niesklasyfikowane SkyRC

- Niesklasyfikowane Waring Commercial

- Niesklasyfikowane Corel

- Niesklasyfikowane SE Electronics

- Niesklasyfikowane Ubiquiti Networks

- Niesklasyfikowane Western Digital

- Niesklasyfikowane Princeton Tec

- Niesklasyfikowane Lindell Audio

- Niesklasyfikowane Verbatim

- Niesklasyfikowane Baby Annabell

- Niesklasyfikowane Caple

- Niesklasyfikowane Taylor

- Niesklasyfikowane Duronic

- Niesklasyfikowane ModeCom

- Niesklasyfikowane Nivona

- Niesklasyfikowane Smoby

- Niesklasyfikowane Smart-AVI

- Niesklasyfikowane Maximum

- Niesklasyfikowane Omega

- Niesklasyfikowane Axagon

- Niesklasyfikowane MXL

- Niesklasyfikowane Cameo

- Niesklasyfikowane Christopeit

- Niesklasyfikowane Comfee

- Niesklasyfikowane Medel

- Niesklasyfikowane Fein

- Niesklasyfikowane Mattel

- Niesklasyfikowane Jumbo

- Niesklasyfikowane Barco

- Niesklasyfikowane Goobay

- Niesklasyfikowane Sagemcom

- Niesklasyfikowane Optex

- Niesklasyfikowane GoPro

- Niesklasyfikowane Bush

- Niesklasyfikowane Siméo

- Niesklasyfikowane ThinkFun

- Niesklasyfikowane Schwaiger

- Niesklasyfikowane New Pol

- Niesklasyfikowane Promise Technology

- Niesklasyfikowane Sharkoon

- Niesklasyfikowane Eheim

- Niesklasyfikowane Watson

- Niesklasyfikowane Saramonic

- Niesklasyfikowane Oase

- Niesklasyfikowane Pro-User

- Niesklasyfikowane Mean Well

- Niesklasyfikowane Gravity

- Niesklasyfikowane Kenmore

- Niesklasyfikowane Kaiser

- Niesklasyfikowane Equip

- Niesklasyfikowane Loewe

- Niesklasyfikowane DeepCool

- Niesklasyfikowane Bluesound

- Niesklasyfikowane Zephyr

- Niesklasyfikowane Michelin

- Niesklasyfikowane Boso

- Niesklasyfikowane Kemo

- Niesklasyfikowane Breville

- Niesklasyfikowane Swift

- Niesklasyfikowane Terraillon

- Niesklasyfikowane Sera

- Niesklasyfikowane Allibert

- Niesklasyfikowane Aerotec

- Niesklasyfikowane GA.MA

- Niesklasyfikowane Juniper

- Niesklasyfikowane Deaf Bonce

- Niesklasyfikowane Sangean

- Niesklasyfikowane BORA

- Niesklasyfikowane Cudy

- Niesklasyfikowane VOX

- Niesklasyfikowane QNAP

- Niesklasyfikowane Ferm

- Niesklasyfikowane COLBOR

- Niesklasyfikowane Insignia

- Niesklasyfikowane AVer

- Niesklasyfikowane AYA

- Niesklasyfikowane Pelgrim

- Niesklasyfikowane Walrus Audio

- Niesklasyfikowane Ambient Weather

- Niesklasyfikowane Veripart

- Niesklasyfikowane Apricorn

- Niesklasyfikowane Esperanza

- Niesklasyfikowane Playtive

- Niesklasyfikowane Arris

- Niesklasyfikowane SVS

- Niesklasyfikowane Navman

- Niesklasyfikowane Chenbro Micom

- Niesklasyfikowane HTC

- Niesklasyfikowane Gabor

- Niesklasyfikowane ZKTeco

- Niesklasyfikowane Netis

- Niesklasyfikowane Frilec

- Niesklasyfikowane Akuvox

- Niesklasyfikowane Benavent

- Niesklasyfikowane Jane

- Niesklasyfikowane Hager

- Niesklasyfikowane Extech

- Niesklasyfikowane NANO Modules

- Niesklasyfikowane Elation

- Niesklasyfikowane GVM

- Niesklasyfikowane Ravensburger

- Niesklasyfikowane TomTom

- Niesklasyfikowane Shark

- Niesklasyfikowane TSC

- Niesklasyfikowane True

- Niesklasyfikowane 3M

- Niesklasyfikowane ECS

- Niesklasyfikowane Franklin

- Niesklasyfikowane Magivaac

- Niesklasyfikowane Victrola

- Niesklasyfikowane Nilfisk

- Niesklasyfikowane Tower

- Niesklasyfikowane XPG

- Niesklasyfikowane Elta

- Niesklasyfikowane Orima

- Niesklasyfikowane Yukon

- Niesklasyfikowane Mac Audio

- Niesklasyfikowane Vakoss

- Niesklasyfikowane Infinity

- Niesklasyfikowane Pentair

- Niesklasyfikowane McIntosh

- Niesklasyfikowane Advance Acoustic

- Niesklasyfikowane Solis

- Niesklasyfikowane Revel

- Niesklasyfikowane Junkers

- Niesklasyfikowane Denver

- Niesklasyfikowane Harley Benton

- Niesklasyfikowane Anker

- Niesklasyfikowane Testboy

- Niesklasyfikowane Pentax

- Niesklasyfikowane Bushnell

- Niesklasyfikowane Horizon Fitness

- Niesklasyfikowane Berger & Schröter

- Niesklasyfikowane Allnet

- Niesklasyfikowane Kernau

- Niesklasyfikowane Veritas

- Niesklasyfikowane Dynacord

- Niesklasyfikowane Aspes

- Niesklasyfikowane Albrecht

- Niesklasyfikowane Marshall Electronics

- Niesklasyfikowane Orion

- Niesklasyfikowane Ashly

- Niesklasyfikowane DCS

- Niesklasyfikowane Hitachi

- Niesklasyfikowane Postium

- Niesklasyfikowane Weller

- Niesklasyfikowane Herkules

- Niesklasyfikowane Blumfeldt

- Niesklasyfikowane Futurelight

- Niesklasyfikowane Yale

- Niesklasyfikowane JIMMY

- Niesklasyfikowane FED

- Niesklasyfikowane InfaSecure

- Niesklasyfikowane Fender

- Niesklasyfikowane Winix

- Niesklasyfikowane Hertz

- Niesklasyfikowane Em-Trak

- Niesklasyfikowane Nitecore

- Niesklasyfikowane InLine

- Niesklasyfikowane Inter-M

- Niesklasyfikowane Kali Audio

- Niesklasyfikowane Rapoo

- Niesklasyfikowane Tracer

- Niesklasyfikowane Salton

- Niesklasyfikowane Ventura

- Niesklasyfikowane Polisport

- Niesklasyfikowane Stabila

- Niesklasyfikowane IStarUSA

- Niesklasyfikowane Joby

- Niesklasyfikowane Technika

- Niesklasyfikowane Emerson

- Niesklasyfikowane Seiki

- Niesklasyfikowane SereneLife

- Niesklasyfikowane JennAir

- Niesklasyfikowane Kyoritsu

- Niesklasyfikowane Pfaff

- Niesklasyfikowane Craftsman

- Niesklasyfikowane Silverstone

- Niesklasyfikowane Mooer

- Niesklasyfikowane Ernitec

- Niesklasyfikowane AKG

- Niesklasyfikowane Vemer

- Niesklasyfikowane Frigidaire

- Niesklasyfikowane CyberPower

- Niesklasyfikowane Azden

- Niesklasyfikowane Galanz

- Niesklasyfikowane FeiyuTech

- Niesklasyfikowane AVerMedia

- Niesklasyfikowane Roccat

- Niesklasyfikowane Olight

- Niesklasyfikowane Barazza

- Niesklasyfikowane Busch-Jaeger

- Niesklasyfikowane Magnus

- Niesklasyfikowane EcoFlow

- Niesklasyfikowane RCA

- Niesklasyfikowane Klein Tools

- Niesklasyfikowane OWC

- Niesklasyfikowane MEE Audio

- Niesklasyfikowane Black Diamond

- Niesklasyfikowane AJA

- Niesklasyfikowane Electro Harmonix

- Niesklasyfikowane KRK

- Niesklasyfikowane MBM

- Niesklasyfikowane Scotsman

- Niesklasyfikowane Genius

- Niesklasyfikowane Marvel

- Niesklasyfikowane Media-Tech

- Niesklasyfikowane Levenhuk

- Niesklasyfikowane Atlas Sound

- Niesklasyfikowane IOTAVX

- Niesklasyfikowane Fieldmann

- Niesklasyfikowane Summit

- Niesklasyfikowane Homelite

- Niesklasyfikowane Gemini

- Niesklasyfikowane BenQ

- Niesklasyfikowane Trevi

- Niesklasyfikowane Technaxx

- Niesklasyfikowane Atlona

- Niesklasyfikowane Elektrobock

- Niesklasyfikowane Thermaltake

- Niesklasyfikowane Amer

- Niesklasyfikowane Hunter

- Niesklasyfikowane Fibaro

- Niesklasyfikowane Sirius

- Niesklasyfikowane Simrad

- Niesklasyfikowane Salus

- Niesklasyfikowane ENTES

- Niesklasyfikowane Tams Elektronik

- Niesklasyfikowane Nintendo

- Niesklasyfikowane Lexibook

- Niesklasyfikowane Soundskins

- Niesklasyfikowane Ridgid

- Niesklasyfikowane Foster

- Niesklasyfikowane Hammond

- Niesklasyfikowane Minn Kota

- Niesklasyfikowane Shindaiwa

- Niesklasyfikowane GPX

- Niesklasyfikowane Gefen

- Niesklasyfikowane Hansgrohe

- Niesklasyfikowane Lanaform

- Niesklasyfikowane Gardenline

- Niesklasyfikowane Martin

- Niesklasyfikowane Hanwha

- Niesklasyfikowane Rommelsbacher

- Niesklasyfikowane American International

- Niesklasyfikowane Ixxat

- Niesklasyfikowane Overmax

- Niesklasyfikowane SEADA

- Niesklasyfikowane Vivanco

- Niesklasyfikowane EQ-3

- Niesklasyfikowane Inkbird

- Niesklasyfikowane Fishman

- Niesklasyfikowane Leifheit

- Niesklasyfikowane Eurochron

- Niesklasyfikowane Radial Engineering

- Niesklasyfikowane PowerPlus

- Niesklasyfikowane Fulgor Milano

- Niesklasyfikowane Quantum

- Niesklasyfikowane MDT

- Niesklasyfikowane Kelvinator

- Niesklasyfikowane Bebe Confort

- Niesklasyfikowane Grandstream

- Niesklasyfikowane Alpha Tools

- Niesklasyfikowane Arturia

- Niesklasyfikowane Lectrosonics

- Niesklasyfikowane Gaggenau

- Niesklasyfikowane Asaklitt

- Niesklasyfikowane Sencor

- Niesklasyfikowane Emko

- Niesklasyfikowane BDI

- Niesklasyfikowane Definitive Technology

- Niesklasyfikowane Ground Zero

- Niesklasyfikowane Noxon

- Niesklasyfikowane Polsen

- Niesklasyfikowane Vonroc

- Niesklasyfikowane Mistral

- Niesklasyfikowane Elica

- Niesklasyfikowane Eversolo

- Niesklasyfikowane Tamron

- Niesklasyfikowane Spear & Jackson

- Niesklasyfikowane Raymarine

- Niesklasyfikowane Powerfix

- Niesklasyfikowane HiKOKI

- Niesklasyfikowane Workzone

- Niesklasyfikowane Insta360

- Niesklasyfikowane Evenflo

- Niesklasyfikowane McCulloch

- Niesklasyfikowane Tempo

- Niesklasyfikowane Nabo

- Niesklasyfikowane EasyMaxx

- Niesklasyfikowane Stinger

- Niesklasyfikowane Dreadbox

- Niesklasyfikowane PowerBass

- Niesklasyfikowane Elo

- Niesklasyfikowane Avanti

- Niesklasyfikowane BABY Born

- Niesklasyfikowane Seaward

- Niesklasyfikowane Revlon

- Niesklasyfikowane Power Dynamics

- Niesklasyfikowane Blackmagic Design

- Niesklasyfikowane AEA

- Niesklasyfikowane Asko

- Niesklasyfikowane Kanto

- Niesklasyfikowane Ikan

- Niesklasyfikowane Alecto

- Niesklasyfikowane Vacmaster

- Niesklasyfikowane Kathrein

- Niesklasyfikowane Kalorik

- Niesklasyfikowane Avidsen

- Niesklasyfikowane Binatone

- Niesklasyfikowane Rockford Fosgate

- Niesklasyfikowane Domyos

- Niesklasyfikowane DOD

- Niesklasyfikowane Suntec

- Niesklasyfikowane Steinberg

- Niesklasyfikowane Impact

- Niesklasyfikowane Be Quiet!

- Niesklasyfikowane Microboards

- Niesklasyfikowane JUNG

- Niesklasyfikowane Xtorm

- Niesklasyfikowane Eaton

- Niesklasyfikowane Carrier

- Niesklasyfikowane Burg Wächter

- Niesklasyfikowane Hammer

- Niesklasyfikowane Nextbase

- Niesklasyfikowane Lund

- Niesklasyfikowane Honey-Can-Do

- Niesklasyfikowane Foscam

- Niesklasyfikowane Lumens

- Niesklasyfikowane Eizo

- Niesklasyfikowane Senal

- Niesklasyfikowane TOA

- Niesklasyfikowane Newland

- Niesklasyfikowane Byron

- Niesklasyfikowane Monacor

- Niesklasyfikowane Esatto

- Niesklasyfikowane Aputure

- Niesklasyfikowane HQ Power

- Niesklasyfikowane Signature

- Niesklasyfikowane Ferplast

- Niesklasyfikowane Daewoo

- Niesklasyfikowane ADE

- Niesklasyfikowane Hotone

- Niesklasyfikowane Cosori

- Niesklasyfikowane X-Sense

- Niesklasyfikowane Neutrik

- Niesklasyfikowane Tannoy

- Niesklasyfikowane Livington

- Niesklasyfikowane Electro-Voice

- Niesklasyfikowane Anthem

- Niesklasyfikowane Dörr

- Niesklasyfikowane Consul

- Niesklasyfikowane Tascam

- Niesklasyfikowane Etekcity

- Niesklasyfikowane RME

- Niesklasyfikowane Metz

- Niesklasyfikowane Laser

- Niesklasyfikowane Wiha

- Niesklasyfikowane M-e

- Niesklasyfikowane Lervia

- Niesklasyfikowane WAGAN

- Niesklasyfikowane Kunft

- Niesklasyfikowane Robinhood

- Niesklasyfikowane Tetra

- Niesklasyfikowane Grunkel

- Niesklasyfikowane SLV

- Niesklasyfikowane H-Tronic

- Niesklasyfikowane Sonnet

- Niesklasyfikowane Novation

- Niesklasyfikowane Silver Cross

- Niesklasyfikowane Vicoustic

- Niesklasyfikowane Zibro

- Niesklasyfikowane Alphatronics

- Niesklasyfikowane Havis

- Niesklasyfikowane Becken

- Niesklasyfikowane JAYS

- Niesklasyfikowane AudioControl

- Niesklasyfikowane Karma

- Niesklasyfikowane Scandomestic

- Niesklasyfikowane NOCO

- Niesklasyfikowane EVE

- Niesklasyfikowane OKAY

- Niesklasyfikowane API Audio

- Niesklasyfikowane Bahr

- Niesklasyfikowane Socket Mobile

- Niesklasyfikowane Smartwares

- Niesklasyfikowane Elgato

- Niesklasyfikowane Traeger

- Niesklasyfikowane Magmatic

- Niesklasyfikowane Porter-Cable

- Niesklasyfikowane Noctua

- Niesklasyfikowane Masport

- Niesklasyfikowane Metabo

- Niesklasyfikowane GVision

- Niesklasyfikowane ProfiCare

- Niesklasyfikowane Audiolab

- Niesklasyfikowane Bretford

- Niesklasyfikowane Galcon

- Niesklasyfikowane Guzzanti

- Niesklasyfikowane Vocopro

- Niesklasyfikowane Technical Pro

- Niesklasyfikowane Adj

- Niesklasyfikowane CM Storm

- Niesklasyfikowane Mauser

- Niesklasyfikowane MEPROLIGHT

- Niesklasyfikowane Lagrange

- Niesklasyfikowane Lamax

- Niesklasyfikowane Absco

- Niesklasyfikowane Bestgreen

- Niesklasyfikowane WiiM

- Niesklasyfikowane AkYtec

- Niesklasyfikowane Wachendorff

- Niesklasyfikowane SPL

- Niesklasyfikowane SureFire

- Niesklasyfikowane ISi

- Niesklasyfikowane Cyrus

- Niesklasyfikowane Gold Note

- Niesklasyfikowane SolaX Power

- Niesklasyfikowane Ketron

- Niesklasyfikowane ETC

- Niesklasyfikowane EZ Dupe

- Niesklasyfikowane IBEAM

- Niesklasyfikowane Terratec

- Niesklasyfikowane Gastronoma

- Niesklasyfikowane Pinolino

- Niesklasyfikowane Transcend

- Niesklasyfikowane Edilkamin

- Niesklasyfikowane Axxess

- Niesklasyfikowane Dualit

- Niesklasyfikowane Kern

- Niesklasyfikowane Crunch

- Niesklasyfikowane Wilson

- Niesklasyfikowane Goki

- Niesklasyfikowane Zoofari

- Niesklasyfikowane EGO

- Niesklasyfikowane WilTec

- Niesklasyfikowane Toro

- Niesklasyfikowane AstralPool

- Niesklasyfikowane ABC Design

- Niesklasyfikowane Müller

- Niesklasyfikowane Cotech

- Niesklasyfikowane Gre

- Niesklasyfikowane Britax

- Niesklasyfikowane Humminbird

- Niesklasyfikowane Dataflex

- Niesklasyfikowane Dormakaba

- Niesklasyfikowane Stairville

- Niesklasyfikowane Snom

- Niesklasyfikowane Elmo

- Niesklasyfikowane Vitek

- Niesklasyfikowane Skil

- Niesklasyfikowane Xvive

- Niesklasyfikowane Geneva

- Niesklasyfikowane Miomare

- Niesklasyfikowane Alfatron

- Niesklasyfikowane Anton/Bauer

- Niesklasyfikowane Sound Devices

- Niesklasyfikowane Eurom

- Niesklasyfikowane Beha-Amprobe

- Niesklasyfikowane Sebo

- Niesklasyfikowane Enermax

- Niesklasyfikowane Clas Ohlson

- Niesklasyfikowane Savio

- Niesklasyfikowane TechBite

- Niesklasyfikowane RADEMACHER

- Niesklasyfikowane Blackburn

- Niesklasyfikowane Salicru

- Niesklasyfikowane Laserliner

- Niesklasyfikowane Zotac

- Niesklasyfikowane Cocraft

- Niesklasyfikowane Lupine

- Niesklasyfikowane Reflexion

- Niesklasyfikowane Megasat

- Niesklasyfikowane Kopp

- Niesklasyfikowane Hikmicro

- Niesklasyfikowane Maytronics

- Niesklasyfikowane Crosley

- Niesklasyfikowane TensCare

- Niesklasyfikowane Varta

- Niesklasyfikowane Nutrichef

- Niesklasyfikowane Constructa

- Niesklasyfikowane Proline

- Niesklasyfikowane Atomos

- Niesklasyfikowane Adventuridge

- Niesklasyfikowane Casa Deco

- Niesklasyfikowane EXIT

- Niesklasyfikowane HK Audio

- Niesklasyfikowane Euromaid

- Niesklasyfikowane Reloop

- Niesklasyfikowane Primewire

- Niesklasyfikowane Lorelli

- Niesklasyfikowane Cherry

- Niesklasyfikowane Greenworks

- Niesklasyfikowane Rittal

- Niesklasyfikowane BSS Audio

- Niesklasyfikowane Newstar

- Niesklasyfikowane Oreck

- Niesklasyfikowane Timbersled

- Niesklasyfikowane I.safe Mobile

- Niesklasyfikowane Artsound

- Niesklasyfikowane Chandler

- Niesklasyfikowane Flama

- Niesklasyfikowane Sevenoak

- Niesklasyfikowane Vivitar

- Niesklasyfikowane Areca

- Niesklasyfikowane Belkin

- Niesklasyfikowane SWIT

- Niesklasyfikowane Zeiss

- Niesklasyfikowane Bebob

- Niesklasyfikowane Morley

- Niesklasyfikowane Generac

- Niesklasyfikowane Kramer

- Niesklasyfikowane Gen Energy

- Niesklasyfikowane Lian Li

- Niesklasyfikowane Kahayan

- Niesklasyfikowane Profoto

- Niesklasyfikowane Wimberley

- Niesklasyfikowane Kopul

- Niesklasyfikowane Analog Way

- Niesklasyfikowane BZBGear

- Niesklasyfikowane K&M

- Niesklasyfikowane RGBlink

- Niesklasyfikowane Glide Gear

- Niesklasyfikowane Hosa

- Niesklasyfikowane Vortex

- Niesklasyfikowane Cranborne Audio

- Niesklasyfikowane SmallRig

- Niesklasyfikowane ToughTested

- Niesklasyfikowane Arkon

- Niesklasyfikowane Trijicon

- Niesklasyfikowane Xcellon

- Niesklasyfikowane Murideo

- Niesklasyfikowane Intellijel

- Niesklasyfikowane CEDAR

- Niesklasyfikowane Rupert Neve Designs

- Niesklasyfikowane Pawa

- Niesklasyfikowane Erica Synths

- Niesklasyfikowane Key Digital

- Niesklasyfikowane Robus

- Niesklasyfikowane Ideal

- Niesklasyfikowane Apantac

- Niesklasyfikowane AMX

- Niesklasyfikowane Rosco

- Niesklasyfikowane Scancool

- Niesklasyfikowane JILONG

- Niesklasyfikowane OBH Nordica

- Niesklasyfikowane AENO

- Niesklasyfikowane ABB

- Niesklasyfikowane SRS

- Niesklasyfikowane Thermador

- Niesklasyfikowane Wolfcraft

- Niesklasyfikowane Budda

- Niesklasyfikowane Soler & Palau

- Niesklasyfikowane Goodis

- Niesklasyfikowane Bestron

- Niesklasyfikowane Eura

- Niesklasyfikowane Optimum

- Niesklasyfikowane Atosa

- Niesklasyfikowane HiLook

- Niesklasyfikowane Rotel

- Niesklasyfikowane Lexmark

- Niesklasyfikowane Atlas

- Niesklasyfikowane Profile

- Niesklasyfikowane Sensiplast

- Niesklasyfikowane Swan

- Niesklasyfikowane Brondi

- Niesklasyfikowane Fysic

- Niesklasyfikowane Wiko

- Niesklasyfikowane A.O. Smith

- Niesklasyfikowane Dangerous Music

- Niesklasyfikowane Lumantek

- Niesklasyfikowane Kluge

- Niesklasyfikowane Aduro

- Niesklasyfikowane Alpina

- Niesklasyfikowane Airlux

- Niesklasyfikowane Aligator

- Niesklasyfikowane Ambrogio

- Niesklasyfikowane Allied Telesis

- Niesklasyfikowane Alienware

- Niesklasyfikowane Amfra

- Niesklasyfikowane Alcon

- Niesklasyfikowane A4tech

- Niesklasyfikowane Ampeg

- Niesklasyfikowane Amplicom

- Niesklasyfikowane Amprobe

- Niesklasyfikowane Archos

- Niesklasyfikowane Argon

- Niesklasyfikowane American Audio

- Niesklasyfikowane Aquapur

- Niesklasyfikowane Devialet

- Niesklasyfikowane KDK

- Niesklasyfikowane IFi Audio

- Niesklasyfikowane Crosscall

- Niesklasyfikowane Cabasse

- Niesklasyfikowane Amiko

- Niesklasyfikowane Aeris

- Niesklasyfikowane Ascom

- Niesklasyfikowane Alpen Kreuzer

- Niesklasyfikowane ACME

- Niesklasyfikowane Reflecta

- Niesklasyfikowane Argus

- Niesklasyfikowane ATN

- Niesklasyfikowane Ziggo

- Niesklasyfikowane Intermatic

- Niesklasyfikowane Flamingo

- Niesklasyfikowane Toolland

- Niesklasyfikowane Brennenstuhl

- Niesklasyfikowane MJX

- Niesklasyfikowane Hirschmann

- Niesklasyfikowane Kruidvat

- Niesklasyfikowane Audison

- Niesklasyfikowane Proteca

- Niesklasyfikowane Toorx

- Niesklasyfikowane Body Solid

- Niesklasyfikowane Tryton

- Niesklasyfikowane Oceanic

- Niesklasyfikowane Korona

- Niesklasyfikowane Saturn

- Niesklasyfikowane Tiger

- Niesklasyfikowane Progress

- Niesklasyfikowane Meradiso

- Niesklasyfikowane BH Fitness

- Niesklasyfikowane Tevion

- Niesklasyfikowane GPO

- Niesklasyfikowane Lucide

- Niesklasyfikowane Parisot

- Niesklasyfikowane Caliber

- Niesklasyfikowane Bellini

- Niesklasyfikowane Eminent

- Niesklasyfikowane Pressalit

- Niesklasyfikowane Oster

- Niesklasyfikowane Kichler

- Niesklasyfikowane VAX

- Niesklasyfikowane Vestel

- Niesklasyfikowane Sinbo

- Niesklasyfikowane Jata

- Niesklasyfikowane VirtuFit

- Niesklasyfikowane Fritel

- Niesklasyfikowane Ordex

- Niesklasyfikowane Itho

- Niesklasyfikowane Targus

- Niesklasyfikowane Q-CONNECT

- Niesklasyfikowane Sicce

- Niesklasyfikowane Outwell

- Niesklasyfikowane Sitecom

- Niesklasyfikowane United Office

- Niesklasyfikowane Monogram

- Niesklasyfikowane Maxdata

- Niesklasyfikowane Hard Head

- Niesklasyfikowane Exibel

- Niesklasyfikowane Logik

- Niesklasyfikowane Easy Camp

- Niesklasyfikowane Energy Sistem

- Niesklasyfikowane Orbit

- Niesklasyfikowane Auto Joe

- Niesklasyfikowane Fortinet

- Niesklasyfikowane Youin

- Niesklasyfikowane Telestar

- Niesklasyfikowane Valore

- Niesklasyfikowane Accucold

- Niesklasyfikowane Sun Joe

- Niesklasyfikowane Perfecta

- Niesklasyfikowane Doro

- Niesklasyfikowane Sagem

- Niesklasyfikowane Cricut

- Niesklasyfikowane Hähnel

- Niesklasyfikowane EWT

- Niesklasyfikowane Enduro

- Niesklasyfikowane Aukey

- Niesklasyfikowane Ernesto

- Niesklasyfikowane KlikaanKlikuit

- Niesklasyfikowane Easypix

- Niesklasyfikowane Ei Electronics

- Niesklasyfikowane Simplified MFG

- Niesklasyfikowane Mellerware

- Niesklasyfikowane Silva

- Niesklasyfikowane Tacklife

- Niesklasyfikowane Energenie

- Niesklasyfikowane Heinner

- Niesklasyfikowane Termozeta

- Niesklasyfikowane Bella

- Niesklasyfikowane Palson

- Niesklasyfikowane Eldom

- Niesklasyfikowane Valeton

- Niesklasyfikowane Jocca

- Niesklasyfikowane Nilox

- Niesklasyfikowane Tiptop Audio

- Niesklasyfikowane Sonos

- Niesklasyfikowane Summit Audio

- Niesklasyfikowane SKS

- Niesklasyfikowane Musway

- Niesklasyfikowane Kensington

- Niesklasyfikowane Nautilus

- Niesklasyfikowane Cresta

- Niesklasyfikowane Maxxmee

- Niesklasyfikowane Brigmton

- Niesklasyfikowane Sunstech

- Niesklasyfikowane Smith & Wesson

- Niesklasyfikowane Reich

- Niesklasyfikowane Defy

- Niesklasyfikowane Stiebel Eltron

- Niesklasyfikowane DeLock

- Niesklasyfikowane Avalon

- Niesklasyfikowane Plant Craft

- Niesklasyfikowane Dubatti

- Niesklasyfikowane Bionaire

- Niesklasyfikowane Sylvania

- Niesklasyfikowane Campomatic

- Niesklasyfikowane Patton

- Niesklasyfikowane Igloo

- Niesklasyfikowane Senco

- Niesklasyfikowane Tork

- Niesklasyfikowane Techly

- Niesklasyfikowane Vaude

- Niesklasyfikowane GlobalTronics

- Niesklasyfikowane Sunny

- Niesklasyfikowane Inglesina

- Niesklasyfikowane BBB

- Niesklasyfikowane BlueBuilt

- Niesklasyfikowane Gazelle

- Niesklasyfikowane Nibe

- Niesklasyfikowane Damixa

- Niesklasyfikowane Da-Lite

- Niesklasyfikowane Trebs

- Niesklasyfikowane Ednet

- Niesklasyfikowane Luxor

- Niesklasyfikowane Bowflex

- Niesklasyfikowane Visage

- Niesklasyfikowane Celestron

- Niesklasyfikowane CaterCool

- Niesklasyfikowane Matrox

- Niesklasyfikowane Rangemaster

- Niesklasyfikowane Maktec

- Niesklasyfikowane Connect IT

- Niesklasyfikowane Steren

- Niesklasyfikowane Eico

- Niesklasyfikowane Hansa

- Niesklasyfikowane Nero

- Niesklasyfikowane Kubo

- Niesklasyfikowane Exagerate

- Niesklasyfikowane Air King

- Niesklasyfikowane Tanaka

- Niesklasyfikowane Gossen

- Niesklasyfikowane Elba

- Niesklasyfikowane Flir

- Niesklasyfikowane Paidi

- Niesklasyfikowane KiddyGuard

- Niesklasyfikowane Livarno

- Niesklasyfikowane Soehnle

- Niesklasyfikowane Barkan

- Niesklasyfikowane Coby

- Niesklasyfikowane Royal Sovereign

- Niesklasyfikowane King

- Niesklasyfikowane Maxwell

- Niesklasyfikowane AcuRite

- Niesklasyfikowane Envivo

- Niesklasyfikowane Gustavsberg

- Niesklasyfikowane Galaxy Audio

- Niesklasyfikowane ESYLUX

- Niesklasyfikowane Ventus

- Niesklasyfikowane Melinera

- Niesklasyfikowane TOTO

- Niesklasyfikowane Fisher Price

- Niesklasyfikowane Technoline

- Niesklasyfikowane Osann

- Niesklasyfikowane Lindam

- Niesklasyfikowane Goliath

- Niesklasyfikowane Yamato

- Niesklasyfikowane Vivo

- Niesklasyfikowane Dorma

- Niesklasyfikowane Belgacom

- Niesklasyfikowane SEB

- Niesklasyfikowane Malmbergs

- Niesklasyfikowane Phoenix

- Niesklasyfikowane AV:link

- Niesklasyfikowane Power Craft

- Niesklasyfikowane Otolift

- Niesklasyfikowane GBC

- Niesklasyfikowane Prenatal

- Niesklasyfikowane Champion

- Niesklasyfikowane Tvilum

- Niesklasyfikowane Heylo

- Niesklasyfikowane TacTic

- Niesklasyfikowane Nolte

- Niesklasyfikowane G3

- Niesklasyfikowane Peach

- Niesklasyfikowane Trixie

- Niesklasyfikowane Finnlo

- Niesklasyfikowane Lescha

- Niesklasyfikowane Capital Sports

- Niesklasyfikowane Buffalo

- Niesklasyfikowane Vello

- Niesklasyfikowane Jenn-Air

- Niesklasyfikowane R-Vent

- Niesklasyfikowane Woood

- Niesklasyfikowane Audiovox

- Niesklasyfikowane Carpigiani

- Niesklasyfikowane Renegade

- Niesklasyfikowane Davis

- Niesklasyfikowane ICU

- Niesklasyfikowane Daitsu

- Niesklasyfikowane Edesa

- Niesklasyfikowane Farberware

- Niesklasyfikowane Ufesa

- Niesklasyfikowane CasaFan

- Niesklasyfikowane Milectric

- Niesklasyfikowane Vicks

- Niesklasyfikowane Yaesu

- Niesklasyfikowane Walkstool

- Niesklasyfikowane Macally

- Niesklasyfikowane Apogee

- Niesklasyfikowane Arlo

- Niesklasyfikowane Nest

- Niesklasyfikowane Kwantum

- Niesklasyfikowane Olimpia Splendid

- Niesklasyfikowane Safescan

- Niesklasyfikowane Pyle Pro

- Niesklasyfikowane Wehkamp

- Niesklasyfikowane Svedbergs

- Niesklasyfikowane Osprey

- Niesklasyfikowane Bunn

- Niesklasyfikowane Ninebot

- Niesklasyfikowane Siedle

- Niesklasyfikowane Cilio

- Niesklasyfikowane LaCie

- Niesklasyfikowane Itho-Daalderop

- Niesklasyfikowane Maul

- Niesklasyfikowane BabyOno

- Niesklasyfikowane Karibu

- Niesklasyfikowane Pericles

- Niesklasyfikowane Troy-Bilt

- Niesklasyfikowane Laica

- Niesklasyfikowane Rusta

- Niesklasyfikowane Samac

- Niesklasyfikowane Brevi

- Niesklasyfikowane SMA

- Niesklasyfikowane Autotek

- Niesklasyfikowane Hive

- Niesklasyfikowane Brabantia

- Niesklasyfikowane AS - Schwabe

- Niesklasyfikowane Fissler

- Niesklasyfikowane Kayoba

- Niesklasyfikowane Wamsler

- Niesklasyfikowane MB Quart

- Niesklasyfikowane Valcom

- Niesklasyfikowane Switel

- Niesklasyfikowane Bopita

- Niesklasyfikowane FireAngel

- Niesklasyfikowane Duux

- Niesklasyfikowane Chacon

- Niesklasyfikowane Astro

- Niesklasyfikowane Imetec

- Niesklasyfikowane InFocus

- Niesklasyfikowane Bigben

- Niesklasyfikowane Topcraft

- Niesklasyfikowane Kraftwerk

- Niesklasyfikowane Naish

- Niesklasyfikowane Festo

- Niesklasyfikowane Massive

- Niesklasyfikowane Barska

- Niesklasyfikowane Weihrauch Sport

- Niesklasyfikowane Blaze

- Niesklasyfikowane Hombli

- Niesklasyfikowane Martha Stewart

- Niesklasyfikowane Milan

- Niesklasyfikowane Lümme

- Niesklasyfikowane Springfree

- Niesklasyfikowane Ansco

- Niesklasyfikowane Glem Gas

- Niesklasyfikowane Goodram

- Niesklasyfikowane MADE

- Niesklasyfikowane Noma

- Niesklasyfikowane IDance

- Niesklasyfikowane Habitat

- Niesklasyfikowane Body Sculpture

- Niesklasyfikowane Maxview

- Niesklasyfikowane Yongnuo

- Niesklasyfikowane Gamma

- Niesklasyfikowane Proctor Silex

- Niesklasyfikowane Elite

- Niesklasyfikowane Zodiac

- Niesklasyfikowane BOHLT

- Niesklasyfikowane Handicare

- Niesklasyfikowane Simplecom

- Niesklasyfikowane Primo

- Niesklasyfikowane Rocketfish

- Niesklasyfikowane Alba

- Niesklasyfikowane Baninni

- Niesklasyfikowane Naxa

- Niesklasyfikowane Nemef

- Niesklasyfikowane Atlantic

- Niesklasyfikowane RugGear

- Niesklasyfikowane Umidigi

- Niesklasyfikowane Saro

- Niesklasyfikowane Millenium

- Niesklasyfikowane Vogue

- Niesklasyfikowane Grixx

- Niesklasyfikowane Topeak

- Niesklasyfikowane SuperFish

- Niesklasyfikowane Luvion

- Niesklasyfikowane Aqua Joe

- Niesklasyfikowane Innovaphone

- Niesklasyfikowane Intel

- Niesklasyfikowane Mamiya

- Niesklasyfikowane Zuiver

- Niesklasyfikowane Fantec

- Niesklasyfikowane Konig

- Niesklasyfikowane Valueline

- Niesklasyfikowane Active Era

- Niesklasyfikowane Trigano

- Niesklasyfikowane Sweex

- Niesklasyfikowane Busch And Müller

- Niesklasyfikowane Ices

- Niesklasyfikowane Vizio

- Niesklasyfikowane Schuberth

- Niesklasyfikowane Cello

- Niesklasyfikowane RDL

- Niesklasyfikowane Austrian Audio

- Niesklasyfikowane Eberspacher

- Niesklasyfikowane Kress

- Niesklasyfikowane Zehnder

- Niesklasyfikowane Laurastar

- Niesklasyfikowane Mx Onda

- Niesklasyfikowane Wacker Neuson

- Niesklasyfikowane Nûby

- Niesklasyfikowane Xterra

- Niesklasyfikowane Fredenstein

- Niesklasyfikowane Dolmar

- Niesklasyfikowane Invacare

- Niesklasyfikowane Nanni

- Niesklasyfikowane Fuji

- Niesklasyfikowane Swissonic

- Niesklasyfikowane Schütte

- Niesklasyfikowane BRIO

- Niesklasyfikowane Aruba

- Niesklasyfikowane RGV

- Niesklasyfikowane Elkay

- Niesklasyfikowane IHealth

- Niesklasyfikowane Hapro

- Niesklasyfikowane Tamiya

- Niesklasyfikowane Logicom

- Niesklasyfikowane Alfen

- Niesklasyfikowane Sound Machines

- Niesklasyfikowane Team

- Niesklasyfikowane Nikkei

- Niesklasyfikowane Petsafe

- Niesklasyfikowane Nelson

- Niesklasyfikowane TranzX

- Niesklasyfikowane Aviom

- Niesklasyfikowane UPM

- Niesklasyfikowane Happy Plugs

- Niesklasyfikowane Duro

- Niesklasyfikowane T'nB

- Niesklasyfikowane Ematic

- Niesklasyfikowane Finder

- Niesklasyfikowane Levoit

- Niesklasyfikowane Palm

- Niesklasyfikowane QSC

- Niesklasyfikowane Phonak

- Niesklasyfikowane Faber

- Niesklasyfikowane Cardiostrong

- Niesklasyfikowane Hartan

- Niesklasyfikowane Hamax

- Niesklasyfikowane Xavax

- Niesklasyfikowane Emmaljunga

- Niesklasyfikowane Fantini Cosmi

- Niesklasyfikowane X4-Tech

- Niesklasyfikowane ZAZU

- Niesklasyfikowane Countryman

- Niesklasyfikowane Minolta

- Niesklasyfikowane Aerial

- Niesklasyfikowane Victor

- Niesklasyfikowane Zagg

- Niesklasyfikowane ESI

- Niesklasyfikowane Edgestar

- Niesklasyfikowane Orbis

- Niesklasyfikowane ACE

- Niesklasyfikowane Maxicool

- Niesklasyfikowane For_Q

- Niesklasyfikowane Avocor

- Niesklasyfikowane Lanzar

- Niesklasyfikowane DoorBird

- Niesklasyfikowane FoodSaver

- Niesklasyfikowane Vroomshoop

- Niesklasyfikowane McGregor

- Niesklasyfikowane Rain Bird

- Niesklasyfikowane Leitz

- Niesklasyfikowane Nvidia

- Niesklasyfikowane Irritrol

- Niesklasyfikowane Boneco

- Niesklasyfikowane Basbau

- Niesklasyfikowane CaterChef

- Niesklasyfikowane Echowell

- Niesklasyfikowane Kasda

- Niesklasyfikowane Patching Panda

- Niesklasyfikowane NEP

- Niesklasyfikowane Veho

- Niesklasyfikowane Kambrook

- Niesklasyfikowane Nevadent

- Niesklasyfikowane Plum

- Niesklasyfikowane Grasslin

- Niesklasyfikowane Puky

- Niesklasyfikowane GFI System

- Niesklasyfikowane Roadstar

- Niesklasyfikowane Humax

- Niesklasyfikowane Vaddio

- Niesklasyfikowane Berner

- Niesklasyfikowane Swarovski Optik

- Niesklasyfikowane Gira

- Niesklasyfikowane Sachtler

- Niesklasyfikowane Seagate

- Niesklasyfikowane Golden Age Project

- Niesklasyfikowane Britax-Romer

- Niesklasyfikowane Technicolor

- Niesklasyfikowane Bravilor Bonamat

- Niesklasyfikowane Blue

- Niesklasyfikowane Efbe-schott

- Niesklasyfikowane Brinsea

- Niesklasyfikowane Genexis

- Niesklasyfikowane Genelec

- Niesklasyfikowane Maxxter

- Niesklasyfikowane Inspire

- Niesklasyfikowane Apart

- Niesklasyfikowane Venta

- Niesklasyfikowane Anchor Audio

- Niesklasyfikowane 4moms

- Niesklasyfikowane Wolf

- Niesklasyfikowane Dantherm

- Niesklasyfikowane Interlogix

- Niesklasyfikowane Projecta

- Niesklasyfikowane Dnt

- Niesklasyfikowane Lyman

- Niesklasyfikowane Genaray

- Niesklasyfikowane Balance

- Niesklasyfikowane Qualcast

- Niesklasyfikowane Cablexpert

- Niesklasyfikowane Iomega

- Niesklasyfikowane Phil And Teds

- Niesklasyfikowane Tornado

- Niesklasyfikowane Stelton

- Niesklasyfikowane Mr Handsfree

- Niesklasyfikowane Pattfield

- Niesklasyfikowane Joovy

- Niesklasyfikowane Bodum

- Niesklasyfikowane Saitek

- Niesklasyfikowane DAS Audio

- Niesklasyfikowane Vestfrost

- Niesklasyfikowane Leen Bakker

- Niesklasyfikowane OSO

- Niesklasyfikowane Roxio

- Niesklasyfikowane Fito

- Niesklasyfikowane Jotul

- Niesklasyfikowane Shoprider

- Niesklasyfikowane WHALE

- Niesklasyfikowane Shuttle

- Niesklasyfikowane Furuno

- Niesklasyfikowane HQ

- Niesklasyfikowane Max

- Niesklasyfikowane Clage

- Niesklasyfikowane Vorago

- Niesklasyfikowane GMB Gaming

- Niesklasyfikowane Cre8audio

- Niesklasyfikowane Nanlite

- Niesklasyfikowane Kupper

- Niesklasyfikowane Ledger

- Niesklasyfikowane Koenig

- Niesklasyfikowane Contour

- Niesklasyfikowane BakkerElkhuizen

- Niesklasyfikowane Lupilu

- Niesklasyfikowane Outdoorchef

- Niesklasyfikowane Boyo

- Niesklasyfikowane IKRA

- Niesklasyfikowane Turmix

- Niesklasyfikowane Fakir

- Niesklasyfikowane IOttie

- Niesklasyfikowane Verizon

- Niesklasyfikowane Trio Lighting

- Niesklasyfikowane Integra

- Niesklasyfikowane Upo

- Niesklasyfikowane Vitamix

- Niesklasyfikowane Cadel

- Niesklasyfikowane Ipevo

- Niesklasyfikowane Miggo

- Niesklasyfikowane Urrea

- Niesklasyfikowane Iget

- Niesklasyfikowane Emtec

- Niesklasyfikowane Ranex

- Niesklasyfikowane Russound

- Niesklasyfikowane Truper

- Niesklasyfikowane ISDT

- Niesklasyfikowane Debel

- Niesklasyfikowane Abac

- Niesklasyfikowane Stannah

- Niesklasyfikowane Comelit

- Niesklasyfikowane Slik

- Niesklasyfikowane Celly

- Niesklasyfikowane Skan Holz

- Niesklasyfikowane Comica

- Niesklasyfikowane Tommee Tippee

- Niesklasyfikowane Globo

- Niesklasyfikowane EverFocus

- Niesklasyfikowane Audient

- Niesklasyfikowane Adesso

- Niesklasyfikowane Infantino

- Niesklasyfikowane C3

- Niesklasyfikowane EMSA

- Niesklasyfikowane Eurospec

- Niesklasyfikowane Waldbeck

- Niesklasyfikowane Natuzzi

- Niesklasyfikowane Satel

- Niesklasyfikowane Bazooka

- Niesklasyfikowane K&K Sound

- Niesklasyfikowane Dutchbone

- Niesklasyfikowane Fanvil

- Niesklasyfikowane Noise Engineering

- Niesklasyfikowane PAC

- Niesklasyfikowane Beretta

- Niesklasyfikowane Wentronic

- Niesklasyfikowane Peerless

- Niesklasyfikowane Xtreme

- Niesklasyfikowane RAVPower

- Niesklasyfikowane Hooker

- Niesklasyfikowane IHome

- Niesklasyfikowane Luxman

- Niesklasyfikowane Gitzo

- Niesklasyfikowane M-Audio

- Niesklasyfikowane SeaLife

- Niesklasyfikowane Nesco

- Niesklasyfikowane Wago

- Niesklasyfikowane AIC

- Niesklasyfikowane Concept2

- Niesklasyfikowane Brydge

- Niesklasyfikowane Selec

- Niesklasyfikowane Aiphone

- Niesklasyfikowane Tivoli Audio

- Niesklasyfikowane JETI

- Niesklasyfikowane Waves

- Niesklasyfikowane EQ3

- Niesklasyfikowane Karlik

- Niesklasyfikowane Comark

- Niesklasyfikowane Coline

- Niesklasyfikowane N8WERK

- Niesklasyfikowane Petri

- Niesklasyfikowane Calex

- Niesklasyfikowane REV

- Niesklasyfikowane Skullcandy

- Niesklasyfikowane Dymond

- Niesklasyfikowane 4smarts

- Niesklasyfikowane Learning Resources